AMD se enfrenta a la próxima revolución "Chiplet" con su nuevo esquema de red de chips

Los intercaladores de silicio activos podrían hacer que los ordenadores sean más pequeñas y mejores, pero las redes necesitan malla

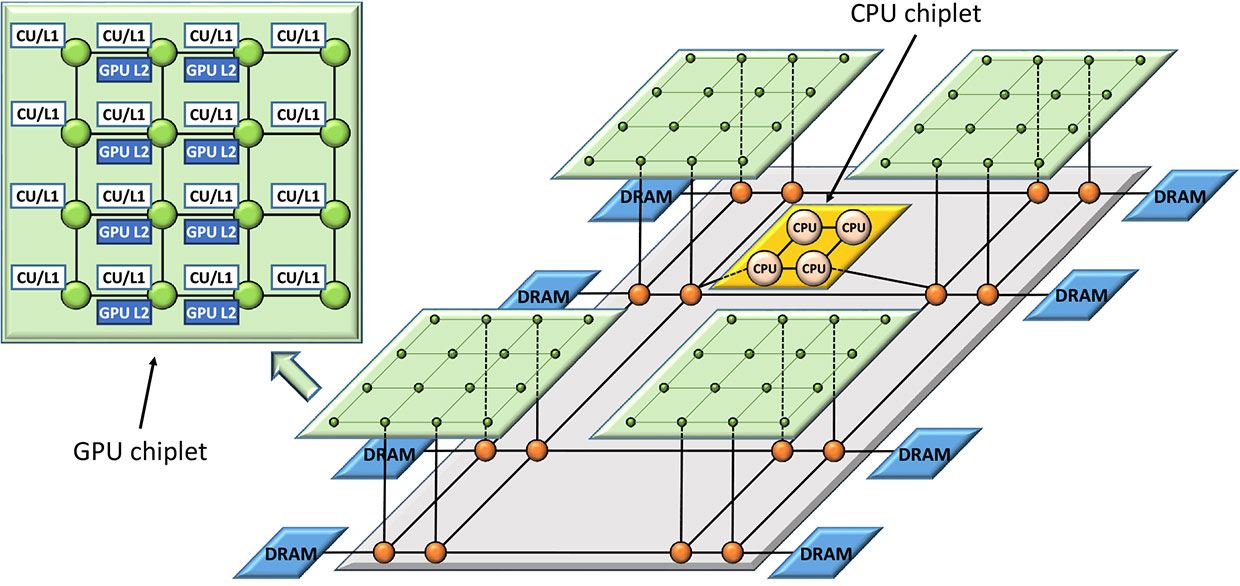

Puede que llegue el momento en que los ordenadores y otros sistemas no estén hechos de chips empaquetados individualmente conectados a una placa base con un circuito impreso, sino de circuitos integrados interconectados en una porción más grande de silicio. Los investigadores han estado desarrollando este concepto llamado "chiplets" con la idea de que permitirá que los datos se muevan más rápido y más libremente para hacer sistemas informáticos más pequeños, más baratos y más integrados. La idea es que las CPU individuales, la memoria y otros sistemas clave se puedan montar en una porción relativamente grande de silicio, llamada intercalador activo, que está lleno de interconexiones y circuitos de enrutamiento.

"En cierto sentido, si esto tuviera éxito, es algo similar a la historia de integración (la Ley de Moore y todo lo demás) que hemos estado hablando durante décadas", dice Gabriel Loh, Fellow Design Engineer en AMD. "Permite a la industria tomar una variedad de componentes del sistema e integrarlos de manera más compacta y más eficiente en conjunto".

Hay (al menos) un problema: aunque el propio sistema de enrutamiento en chip de cada chiplet puede funcionar perfectamente, cuando están todos conectados en la red del intercalador, puede surgir una situación en la que una red intenta enrutar datos de tal manera que el tráfico se produce un atasco que termina por apoderarse del ordenador. "Un punto muerto puede ocurrir básicamente donde tienes un ciclo de mensajes diferentes, todos tratando de competir por el mismo tipo de recursos, lo que hace que todos esperen a los demás", explica Loh.

"Cada uno de esos [chiplets] individuales podría diseñarse para que nunca tengan puntos muertos", dice Loh. "Pero una vez que los junté hay nuevos caminos y nuevas rutas que ningún individuo había planeado con anticipación". Tratar de evitar estos nuevos bloqueos diseñando todos los chiplets junto con una red de intercaladores en particular derrotaría las ventajas de la técnica: los chiplets, por lo tanto, no podían ser diseñados y optimizados fácilmente por equipos separados, y no podían mezclarse y combinarse fácilmente para formar rápidamente nuevos sistemas. En el Simposio Internacional de Arquitectura de ordenadores a principios de este mes, los ingenieros de AMD presentaron una posible solución a este problema inminente.

Un futuro sistema podría contener un chip de CPU y varias GPU, todas conectadas a la misma pieza de silicio habilitado para la red.

El equipo de AMD descubrió que los interbloqueos activos en interpositores activos básicamente desaparecen si se siguen unas pocas reglas simples cuando se diseñan redes en el chip. Estas reglas gobiernan donde se permite que los datos entren y salgan del chip y también restringen las direcciones a las que puede llegar cuando ingresa por primera vez al chip. Sorprendentemente, si sigues esas reglas puedes pretender que todo lo demás en el intercalador -todos los demás chiplets lógicos, la memoria, la propia red del intercalador, todo- es solo un nodo en la red. Sabiendo eso, diferentes equipos de ingenieros pueden diseñar chips sin tener que preocuparse por cómo funcionan las redes en otros chiplets o incluso cómo funciona la red en el intercalador activo.

Puede pasar un tiempo hasta que esto sea necesario. Las llamadas interpolaciones pasivas (silicio que contiene interconexiones pero no circuitos de red) ya están en uso; AMD ha estado usando uno para su serie Radeon R9, por ejemplo. Pero agregar una red inteligente al intercalador podría generar un gran cambio en la forma en que se diseñan los sistemas y en lo que pueden hacer.